# UNIVERSIDADE DO VALE DO RIO DOS SINOS - UNISINOS UNIDADE ACADÊMICA DE PESQUISA E PÓS-GRADUAÇÃO PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA NÍVEL MESTRADO PROFISSIONAL

RENAN DANIEL DIAS MARTINS

PROJETO E ANÁLISE DE CIRCUITOS DE COLETA DE ENERGIA DE RÁDIO FREQUÊNCIA PARA APLICAÇÕES IOT

#### RENAN DANIEL DIAS MARTINS

## PROJETO E ANÁLISE DE CIRCUITOS DE COLETA DE ENERGIA DE RÁDIO FREQUÊNCIA PARA APLICAÇÕES IOT

Dissertação apresentada como requisito parcial para obtenção do título de Mestre em Engenharia Elétrica, pelo Programa de Pós-Graduação em Engenharia Elétrica da Universidade do Vale do Rio dos Sinos - UNISINOS

Orientador: Prof. Dr. Sandro Binsfeld Ferreira

M386m Martins, Renan Daniel Dias.

Projeto e análise de circuitos de coleta de energia de rádio frequência para aplicações IOT / Renan Daniel Dias Martins. -2021.

92 f.: il.; 30 cm.

Dissertação (mestrado) — Universidade do Vale do Rio dos Sinos, Programa de Pós-Graduação em Engenharia Elétrica, 2021.

"Orientador: Prof. Dr. Sandro Binsfeld Ferreira."

- 1. Captação de energia. 2. Circuitos integrados.

- 3. Semicondutores complementares de óxido metálico.

- 4. Radiofrequência. 5. Eficiência de conversão de potência.

I. Título.

CDU 621.3

Dados Internacionais de Catalogação na Publicação (CIP) (Bibliotecária: Amanda Schuster – CRB 10/2517)

Dedico este trabalho àquela que sempre me apoia e incentiva incondicionalmente, Tatiane Texeira.

#### **AGRADECIMENTOS**

Agradeço, primeiramente, à esta instituição de ensino, seu corpo docente, administrativo e diretivo, que sempre buscou e busca proporcionar a melhor experiência universitária para seus estudantes, fundamentada em seus princípios éticos voltados ao desenvolvimento da sociedade e do indivíduo.

Agradeço ao professor Sandro Binsfeld Ferreira pela orientação, paciência e por todo o conhecimento que compartilhou nesta trajetória acadêmica.

Agradeço à HT Micron Semicondutores S.A., que me possibilitou dar mais esse passo em minha trajetória acadêmica, através do Programa de Apoio ao Desenvolvimento tecnológico da Indústria de Semicondutores (PADIS).

Por fim, agradeço à Tatiane Texeira pelo apoio incondicional e pela motivação em todos os momentos dessa jornada.

**RESUMO**

Este trabalho apresenta uma visão geral sobre dispositivos para coleta de energia do

espectro de radiofrequência, apontando vantagens e desvantagens das principais topologias utilizadas, bem como apresentando os pontos mais relevantes para o projeto de sistemas de *Energy Harvesting*. Para demonstrar o funcionamento de um sistema de *Energy Harvesting*, é proposto um circuito para esta finalidade que faz uso de uma antena de RF, uma rede de casamento de impedâncias com circuito ressonante para elevação de tensão de entrada e um retificador em topologia de multiplicador de tensão por acoplamento cruzado de portas modificado. O circuito proposto utiliza dez estágios de multiplicação de tensão e é capaz de fornecer tensão de saída igual a 1,2 V quando alimentado com -26 dBm entre terminais de saída da antena. São demonstradas formas de definir parâmetros de projeto para EH, como tensão de

saída, quantidade de estágios de multiplicação, topologias alternativas, e como encontrar o

ponto ótimo de trabalho do circuito através de simulações. O circuito integrado foi desenvolvido

em tecnologia CMOS TSMC 180 nm e apresenta uma eficiência de conversão de energia (PCE)

Palavras-chave: Energy Harvesting, Circuito Integrado, CMOS, RF, PCE.

máxima de 28,41%.

**ABSTRACT**

This work presents an overview of RF Energy Harvesting devices, pointing out the

advantages and disadvantages of the main topologies used, as well as presenting the most

relevant points for the design of Energy Harvesting systems. To demonstrate the operation of

an Energy Harvesting system, a circuit is proposed for this purpose that makes use of an RF

antenna, an impedance matching network with a resonant circuit for raising the input voltage

and a modified gate cross-coupled charge pump rectifier (CC-CPR). The proposed circuit uses

ten stages of CC-CPR to providing an output voltage equal to 1.2 V when powered with -26

dBm. Ways to define design parameters for EH are demonstrated, such as output voltage,

number stages of rectification, alternative topologies, and how to find the optimal working point

of the circuit through simulations. The integrated circuit was developed in CMOS TSMC

180nm technology and has a maximum power conversion efficiency (PCE) of 28.41%.

**Keywords:** RF Energy Harvesting, IC, CMOS, PCE, CC-CPR.

#### LISTA DE SIGLAS

AM Amplitude Modulation (modulação por amplitude)

BW Bandwidth (largura de banda)

CAD Computer Assisted Design (desenho assistido por computador)

CC Corrente Contínua

CC-CPR Cross Coupled Charge Pump Rectifier (retificador multiplicador de tensão por

chaveamento cruzado)

CI Circuito Integrado

CMOS Complementary Metal Oxide Semiconductor (semicondutor de óxido metálico

complementar)

CVD Chemical Vapor Deposition (deposição química em fase de vapor)

EH Energy Harvesting (captação de energia de fonte conhecida)

ES Energy Scavenging (captação de energia de fonte desconhecida)

GSM Global System for Mobile (Sistema global para dispositivos móveis)

IA Inteligência Artificial

IoT Internet of Things (internet das coisas)

ISM Industrial, Scientific and Medical (industrial, científica e médica)

LDO Low Dropout (baixa queda de tensão – retificadores)

M2M Machine to Machine (máquina para máquina)

MOSFET Metal Oxide Semiconductor Field Effect Transistor (transistor de efeito de

campo de semicondutor de óxido metálico)

NMOS N type Metal Oxide Semiconductor (semicondutor de óxido metálico tipo N)

OS-CPR Orthogonally Switching Charge Pump Rectifier (retificador multiplicador de

tensão com chaveamento ortogonal)

P&G Procter & Gumble

PCE Power Conversion Efficiency (eficiência de conversão de potência)

PDCA Plan, Do, Check, Act (planejar, executar, verificar, agir)

PDK Process Development Kit (pacote de desenvolvimento de processo)

PIB Produto Interno Bruto

PMOS P type Metal Oxide Semiconductor (semicondutor de óxido metálico tipo P)

PMU Power Management Unit (unidade de gerenciamento de energia)

RF Radiofrequência

RFEH Radio Frequency Energy Harvesting (captação de energia de radiofrequência)

RFID Radio Frequency Identification (identificação por radiofrequência)

TSMC Taiwan Semiconductor Manufacturing Company (companhia fabricante de

semicondutores Taiwan)

UV Ultravioleta

VBN Voltage-boosting Network (rede de elevação de tensão)

### SUMÁRIO

| 1     | INTRODUÇÃO                                                         | 17 |

|-------|--------------------------------------------------------------------|----|

| 1.1   | Tema                                                               | 19 |

| 1.2   | Delimitação do tema                                                | 19 |

| 1.3   | Problema                                                           | 19 |

| 1.4   | Objetivos                                                          | 20 |

| 1.4.1 | Objetivo geral                                                     | 20 |

| 1.4.2 | Objetivos específicos                                              | 20 |

| 1.5   | Justificativa                                                      | 20 |

| 2     | FUNDAMENTAÇÃO TEÓRICA                                              | 23 |

| 2.1   | Internet das coisas                                                | 23 |

| 2.2   | Energy Harvesting                                                  | 24 |

| 2.3   | Ondas Eletromagnéticas e Radiofrequência                           | 25 |

| 2.4   | Antenas                                                            | 27 |

| 2.5   | Disponibilidade de energia                                         | 30 |

| 2.6   | Retificadores                                                      | 33 |

| 2.6.1 | Multiplicadores de tensão Dickson e Cockcroft-Walton               | 35 |

| 2.6.2 | Multiplicador de tensão por chaveamento ortogonal (OS-CPR)         | 37 |

| 2.6.3 | Multiplicador de tensão por acoplamento cruzado (CC-CPR)           | 39 |

| 2.7   | Gerenciadores de energia                                           | 44 |

| 2.8   | Armazenadores de energia                                           | 45 |

| 2.9   | Conceitos básicos sobre circuitos integrados CMOS e sua fabricação | 45 |

| 3     | METODOLOGIA                                                        | 55 |

| 3.1   | Especificação dos requisitos                                       | 57 |

| 3.2   | Estudo das topologias                                              | 57 |

| 3.3   | Projeto do circuito, simulação e ajustes                           | 58 |

| 3.4   | Layout                                                             | 61 |

| 3.5   | Simulações                                                         | 63 |

| 4     | ANÁLISE DOS RESULTADOS                                             | 65 |

| 4.1   | Trabalhos correlatos                                               | 80 |

| 5     | CONCLUSÃO                                                          | 83 |

| 5.1   | Sugestões para trabalhos futuros                                   | 84 |

| REFI  | ERÊNCIAS                                                           | 85 |

#### 1 INTRODUÇÃO

Desde a primeira revolução industrial, o ritmo de produção da indústria só aumenta, fomentando o desenvolvimento de novas tecnologias que permitam cada vez tornar as produções mais eficientes e eficazes, reduzindo os custos de produção, os desperdícios e a necessidade de interação humana, como vem acontecendo desde a terceira revolução industrial, com a automatização das produções. Recentemente, entramos na quarta revolução industrial, que está sendo fomentada principalmente pelo desenvolvimento da Indústria 4.0, que consiste não mais na mecanização, alto uso de energia elétrica e automação dos processos produtivos, como nas três primeiras revoluções (LEE; KAO; YANG, 2014), mas no uso da inteligência para gerenciar esses processos. Desta vez, essa inteligência não é mais humana, mas das máquinas. Neste período histórico que vivemos, com processos produtivos cada vez mais complexos e margens de lucro cada vez menores, a capacidade humana de tomada de decisões importantes ao processo não são mais suficientes, tanto em quantidade quanto em velocidade e até mesmo qualidade. Eliciado pela Internet, a Indústria 4.0 permite a comunicação entre humanos e também entre máquinas nos Sistemas Cibernéticos Físicos para adquirir e processar dados e controlar certas tarefas. Isto está transformando radicalmente o desempenho das atividades de manufatura em todo o mundo (SHAMIM et al., 2019).

Decisões precisam ser tomadas a cada segundo em um processo produtivo atual e máquinas são capazes de tomar milhões, talvez bilhões de decisões a cada segundo, tornando o humano defasado nesse quesito. Porém, para que uma máquina seja capaz de tomar essas decisões, ela precisa ser treinada, ensinada a tomá-las. As Inteligências Artificiais (IA) são ferramentas computacionais desenvolvidas para executarem determinadas tarefas e responderem de forma rápida a desvios de processo ou mesmo encontrar soluções para problemas extremamente complexos de forma rápida. Estas respostas rápidas são possíveis devido a quantidade de dados sobre o processo ou atividade que essa IA tem acesso. Esses dados são, geralmente, oriundos de sensores, atuadores e informações pré-carregadas. Com processos extremamente complexos, essa quantidade de dispositivos conectados aumenta significativamente.

Quando há uma quantidade muito grande de dispositivos conectados entre si, interagindo e executando suas funções em uma rede, independentemente da interferência humana, tem-se o que se chamou de Internet das Coisas, ou IoT, da sigla em inglês para *Internet of Things*. Este termo foi usado pela primeira vez em 1999 por Kevin Ashton, em uma apresentação na empresa Procter & Gamble (P&G), enquanto desenvolvia dispositivos de

identificação por radiofrequência (RFID) (ASTHON, 2010). Atualmente, com a complexidade cada vez maior de processos, são necessários muitos dispositivos de sensoriamento para monitorar esses processos, fazendo com que a demanda por dispositivos aumente, forçando o custo individual desses dispositivos a cair, de forma que o sistema se mantenha praticável. Com isso, se faz necessário reduzir os custos de produção e manutanção de cada dispositivo. Formas encontradas para isso são a eliminação de cabos e baterias, que sempre tem custos elevados nesse tipo de projeto.

Além do custo, a evolução tecnológica das baterias, por exemplo, não segue o mesmo ritmo de avanço que a evolução dos sistemas digitais, conforme Pop-Vadean *et al.* (2017), o que causa uma lacuna entre estes setores e acaba limitando a autonomia energética dos projetos. Dessa forma, desenvolver dispositivos capazes de captar a própria energia do ambiente em que estão inseridos é altamente recomendado para a implantação de projetos complexos de IoT.

Circuitos capazes de obter energia do ambiente constantemente e, assim, manterem-se em funcionamento sem a necessidade de intervenção humana reduzem o custo de projeto, o custo de manutenção e, por consequência, permitem que a rede fique cada vez maior, mais inteligente, mais autônoma e mais eficaz. Isso ocorre, pois quanto mais sensores e atuadores, maior é a geração de dados e maior é o controle da rede sobre a atividade ou processo. O *Energy Harvesting* (EH) representa uma solução para alimentar dispositivos remotos usando energia limpa, eliminando a necessidade de baterias e, assim, eliminando um obstáculo para o sucesso da Internet das Coisas, conforme Pop-Vadean et al. (2017).

Este trabalho trata da análise de topologias de coleta de energia do espectro eletromagnético presente nas áreas de atividade humana, como sinais de rádio de telefonia móvel, internet 3G, 4G e Wi-Fi, por exemplo, utilizando a tecnologia CMOS TSMC 180 nm. Cada processo é caracterizado pelo comprimento mínimo de canal, L<sub>mín</sub>; e, assim, por exemplo, em um processo de 180 nm, como o utilizado neste trabalho, o menor transistor tem um comprimento de canal de 180 nm (SEDRA; SMITH, 2007). Dispositivos CMOS são circuitos fundamentais para a eletrônica, tanto analógica quanto digital, estes transistores podem ser utilizados na construção de portas lógicas digitais, bem como na concepção de amplificadores ou chaves eletrônicas. Uma das aplicações mais comuns para estes transistores são os amplificadores. Para Razavi (2016), estes são elementos fundamentais para elevar a tensão, a corrente ou a potência de sinais elétricos. Isso é feito, pois alguns sinais são muito baixos e podem não ser capazes de acionar cargas, ou mesmo podem ser muito sensíveis a ruídos. A aplicação dos transistores CMOS neste trabalho consiste em chaves de passagem ou bloqueio de corrente elétrica, de acordo com o ponto de operação do circuito.

Este trabalho está organizado de forma a apresentar um referencial teórico básico ao entendimento do texto, seguido pela estruturação da metodologia utilizada para o desenvolvimento do trabalho, onde são apresentadas as etapas de execução do projeto. Logo em seguida, são apresentados os resultados obtidos e feita uma discussão sobre eles, levantando pontos relevantes ao conhecimento construído. Então é feita uma comparação entre os resultados obtidos neste trabalho com os resultados obtidos pelas referências bibliográficas utilizadas e por fim são apresentadas as conclusões obtidas com o trabalho e algumas sugestões para trabalhos futuros.

#### 1.1 Tema

Conectar dispositivos físicos ao mundo virtual por meio da internet é o passo atual na escalada tecnológica da humanidade. O uso da IA para tomar decisões importantes em processos e atividades complexas permite aos humanos dedicarem mais tempo para o desenvolvimento de tecnologias ainda mais avançadas. Enquanto isso, máquinas se tornam cada vez mais capazes de tomar decisões por si, gerando ganho de tempo e produtividade em toda a atividade humana, através de inúmeros sensores e atuadores conectados à IA através da rede—que pode ser a internet. O tema deste trabalho é a apresentação de uma forma de autossuficiência energética para os nós mais básicos de uma rede de coisas; os sensores. Eliminando a necessidade de cabos e baterias do sistema, tornando-o menos custoso para implantação e possibilitando um sistema ainda mais robusto, devido ao aumento da quantidade de nós.

#### 1.2 Delimitação do tema

Este trabalho foca na análise e desenvolvimento de circuitos capazes de coletar energia de campos eletromagnéticos do ambiente e convertê-la em energia elétrica capaz de alimentar dispositivos IoT de baixo consumo. A este tipo de captação de energia é dado o nome de *Energy Harvesting (EH)*, sendo os circuitos responsáveis por esta coleta e transformação de energia denominados *Harvesters*.

#### 1.3 Problema

O desenvolvimento acelerado da internet das coisas faz a demanda por dispositivos aumentar, fazendo com que o custo unitário por nós seja forçado a cair. Uma forma de reduzir esse custo nos nós básicos de uma rede IoT é eliminar a dependência de cabos e baterias para alimentação deles. Circuitos capazes de coletar energia através de radiofrequência (RF) são

denominados RFEH (*Radio Frequency Energy Harvester*). Esse conceito de transferência de energia sem fios através de RF foi introduzido por Nikola Tesla em 1900 e chamado de *Wireless Power Transfer (WPT)*, ou Transferência de Energia Sem Fios em português (TESLA, 1900).

#### 1.4 Objetivos

#### 1.4.1 Objetivo geral

Projetar um circuito utilizando tecnologia CMOS capaz de coletar energia eletromagnética na banda ISM (Industrial, Científica e Médica) centrada em 915 MHz para alimentar dispositivos IoT de baixo consumo de energia.

#### 1.4.2 Objetivos específicos

Para o atendimento do objetivo final deste trabalho, algumas metas devem ser alcançadas. A lista abaixo sugere os objetivos específicos para o cumprimento destas metas.

- a) definir os pontos relevantes a serem levados em consideração no projeto de circuitos para coleta de energia em radiofrequência;

- b) definir algum método de avaliação de viabilidade do uso da tecnologia proposta de acordo com o espectro RF disponível;

- c) avaliar as principais topologias utilizadas nesse tipo de circuito, mencionando os prós e contras de cada uma delas, para auxiliar na escolha da topologia adequada para cada tipo de projeto de circuito de *Energy Harvesting*.

#### 1.5 Justificativa

Desenvolver soluções em IoT exige o atendimento a uma gama de exigências. A principal delas é o baixo custo de implantação e manutenção, visto que a quantidade de nós presentes na rede é muito grande. Assim, quanto menor for o custo do nó, maior e mais "inteligente" poderá ser a rede. O principal causador do aumento do custo de um dispositivo conectado à rede é o uso de baterias, pois tem valor elevado para implantação e necessitam de manutenção periódica. Para eliminar esse custo com baterias, bem como o custo com a manutenção delas, o circuito deve ser o mais otimizado possível em termos de consumo energético. O desenvolvimento de circuitos de baixo consumo capazes de coletar energia do ambiente, sem a utilização de fios e sem a necessidade de baterias, torna viável a implementação de redes cada vez maiores e cada

vez mais inteligentes, deixando os limites de suas possibilidades apenas na criatividade e capacidade técnica de seus integradores.

#### 2 FUNDAMENTAÇÃO TEÓRICA

Para melhor compreensão e visão geral sobre o problema que este trabalho busca solucionar, é imprescindível o conhecimento prévio de alguns conceitos e fundamentos básicos sobre o universo que envolve a Internet das Coisas (IoT). A seguir são apresentados, em tópicos, os principais conceitos e elementos que a compõem.

#### 2.1 Internet das coisas

A Internet das coisas não é mais uma visão futurística, mas sim uma realidade, alcançando domínios de aplicação que vão desde casas inteligentes, passando por cidades inteligentes e *e-health*, até a Indústria 4.0 (BRÖRING *et al.*, 2017). Desde a primeira vez em que o termo foi usado em 1999 até os dias atuais, o aumento da pesquisa e o desenvolvimento de aplicações voltadas para a Internet das coisas cresce continuamente, como se pode medir pelo tamanho do mercado de sensores IoT, que se expandiu quase duas vezes e meia de 2012 a 2019, conforme Bedi *et al.* (2018). Esse constante crescimento se dá principalmente pela popularização da Internet das coisas e o barateamento dos nós físicos da rede. Como exemplo, pode-se citar a crescente demanda por produtos de uso doméstico que se conectam à internet, como eletrodomésticos, lâmpadas, eletroeletrônicos em geral e assistentes pessoais.

Além disso, a indústria e o agronegócio também têm investido fortemente na modernização de suas unidades produtivas, visto os ganhos de produtividade que se tornam possíveis com um forte investimento em tecnologia. De acordo com SAP (2016), por exemplo, a integração de dispositivos IoT em uma linha de tratores de um de seus clientes gerou aumento de 100% na confiabilidade dos dados gerados e de 100% na velocidade da informação para a tomada de decisões, o que representa ganhos de produtividade reais no campo, onde está concentrado cerca de 22% do Produto Interno Bruto Brasileiro (PIB).

De forma simplificada, a Internet das coisas é formada sempre que há dois ou mais dispositivos que interagem entre si através da internet, com ou sem interferência humana, em um tipo de comunicação conhecido como *Machine-to-Machine* (M2M) ou Máquina para máquina, em português. Na prática, uma rede IoT bem formulada é composta de sensores para monitorar processos ou atividades, atuadores para executar atividades, algum nível de automação para garantir a autonomia do sistema e um monitoramento através de uma IA, capaz de adequar todo o processo às pequenas variações inerentes ao universo físico da aplicação. Nesta etapa podem ser aplicados conceitos de Aprendizado de Máquina para desenvolver a

robustez de todo o sistema e reduzir a interação humana, gerando resultados mais precisos, mais eficazes, mais efetivos e mais rápidos.

Este tipo de estrutura, conforme se torna mais complexa, acaba exigindo maior quantidade de nós, que podem ser sensores ou atuadores. Estes nós precisam ter o custo unitário inversamente proporcional à quantidade necessária de nós na aplicação para que a implementação e expansão da rede seja possível. Assim, uma das formas de redução de custo do nó é a eliminação do uso de cabos e baterias para energização, deixando o próprio nó responsável por captar a energia necessária para o seu funcionamento. Este processo de coleta de energia é conhecido pelo termo em inglês *Energy Harvesting* (coleta de energia).

#### 2.2 Energy Harvesting

Energy Harvesting (EH) é um conceito utilizado para definir sistemas capazes de coletar a energia disponível no ambiente nas mais diversas formas, como a solar, de vibrações, térmica, cinética, piezoelétrica e de radiofrequência. Um outro conceito que se assemelha a este, o Energy Scavenging (coleta de energia – quando se pretende coletar toda a energia disponível no ambiente de forma não seletiva), é um tipo de sistema com a mesma finalidade do Energy Harvesting – coletar energia do ambiente para alimentar um circuito - porém, enquanto o Harvesting é focado em coletar energia de uma fonte conhecida, o Energy Scavenging (ES) é um tipo de coleta de energia que busca tudo o que está disponível no ambiente para utilização. "O Energy Scavenging refere-se a ambientes onde as fontes ambientais são desconhecidas ou altamente irregulares, enquanto o Energy Harvesting refere-se a situações em que as fontes de energia do ambiente são bem caracterizadas e regulares" (PRIYA e INMAN, 2009). Porém, para manter um sistema operando de forma constante, sem interrupções, o mais indicado é o modelo definido pelo Energy Harvesting, onde as características ambientais são conhecidas, ou mesmo geradas para este fim. Fisicamente, são dispositivos iguais, com funcionamentos equivalentes, mudando apenas o foco, pois geralmente um EH é projetado para se obter o máximo desempenho no ponto de operação, enquanto o ES é otimizado para captar energia em qualquer ponto de operação, ou em uma larga faixa.

Por décadas, as fontes de energia solar e eólica foram exploradas para diversas aplicações. As últimas décadas assistiram a grandes esforços de pesquisa dedicados à diversificação de fontes de energia para alimentar sensores autônomos para redes IoT (PENELLA-LÓPEZ e GASULLA-FORNER, 2011). Com o desenvolvimento da Internet das coisas, novas fontes de energias alternativas em pequena escala estão sendo utilizadas.

Basicamente, pode-se subdividir estas fontes de pequena escala em fontes irradiantes, mecânicas, térmicas, magnéticas e bioquímicas. A maneira de coletar e converter a energia dessas fontes é o que caracteriza o tipo de dispositivo de *Energy Harvesting*. Neste trabalho é abordado o tipo de coletor de energia de radiofrequência (RFEH).

#### 2.3 Ondas Eletromagnéticas e Radiofrequência

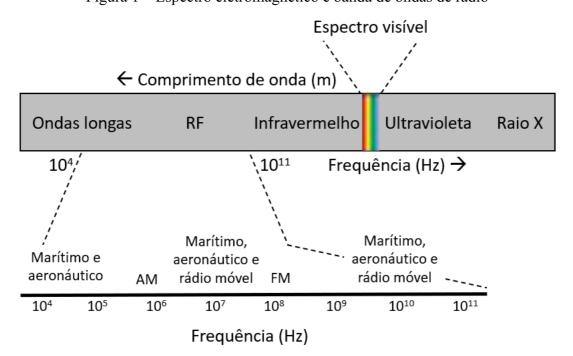

As ondas de rádio existem em praticamente todos os lugares do planeta e do espaço. Todo local habitado por seres humanos apresenta um espectro eletromagnético bastante rico e definido, especialmente nas bandas ocupadas pelas frequências de celular, internet móvel e *Wi-Fi*. A faixa de frequências que abrange este espectro vai de 3 kHz até 300 GHz. Como o próprio nome diz, essa faixa é utilizada, principalmente, por equipamentos de comunicação via rádio. Os mecanismos por trás da propagação de ondas eletromagnéticas são diversos, mas geralmente são atribuídas à reflexão, difração e refração (RAPPAPORT, 2002). A Figura 1 apresenta uma ilustração do espectro eletromagnético, enfatizando a banda de radiofrequência. Canais de televisão e de rádio AM, por exemplo, representam bandas específicas definidas legalmente para fins comerciais ou outros propósitos. Não existem lacunas no espectro eletromagnético (HALLIDAY et al., 2012), o que se observa são bandas com mais ou menos potência sendo irradiada ou captada, dependendo da localização e serviços de rádio utilizados na região.

Figura 1 – Espectro eletromagnético e banda de ondas de rádio

Fonte: Adaptado de Halliday, Resnick e Walker (2012, p. 2).

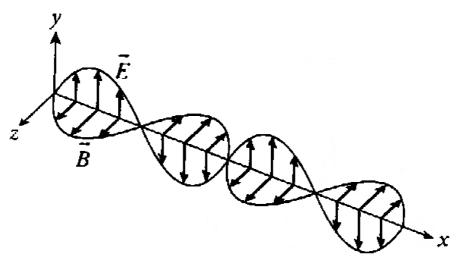

Uma onda eletromagnética pode ser representada graficamente através da combinação de duas outras ondas; uma de campo elétrico e outra de campo magnético. Essas ondas surgem naturalmente quando cargas elétricas se movimentam em qualquer corpo. Cargas em movimento geram campos elétricos variantes, que induzem forças magnéticas sobre a matéria, que por sua vez, acabam formando campos magnéticos proporcionais a estes campos elétricos iniciais. A variação destes dois campos em conjunto gera ondas eletromagnéticas.

Os campos magnético e elétrico que formam uma onda eletromagnética que se propaga particular e positivamente no eixo x, como mostra a Figura 2 podem ser representados através das expressões:

$$\vec{E} = (\vec{r}, t) = E_{max} \sin(kx - \omega t)\hat{y} \tag{1}$$

e

$$\vec{B} = (\vec{r}, t) = B_{m\acute{a}x} \sin(kx - \omega t)\hat{z}$$

(2)

Onde  $k = 2 \pi / \lambda e \omega = 2 \pi f$ .

Figura 2 – Onda eletromagnética

Fonte: Bauer, Westfall e Dias (2012, p. 231).

Apenas é importante salientar que as intensidades de ambos os campos não possuem qualquer dependência com as coordenadas y e z, somente com a coordenada x e com o tempo. Esse tipo de onda, em que os vetores campo elétrico e campo magnético se situam em um mesmo plano, é denominado onda plana. O campo elétrico se encontra inteiramente na direção y, enquanto seu campo magnético encontra-se inteiramente na direção z, ou seja, ambos os campos são perpendiculares à direção de propagação da onda. (BAUER; WESTFALL; DIAS, 2012)

Conforme Hagerty et al (2004, apud Penella-López e Gasulla-Forner, 2011), ondas de rádio são emitidas em *broadcasting* de uma estação de geração ou de antenas de telefonia celular. Geralmente as antenas utilizadas em EH para coleta de energia do ambiente são de *broadband* e polarizadas circularmente. Para Penella-López e Gasulla-Forner (2011), isso se dá pelo fato de haver muitas frequências disponíveis e diferentes polarizações, ou ainda por não conhecer integralmente o espectro de radiofrequências do ambiente. No caso de uso de geradores para alimentação de dispositivos por RF, as bandas industriais, científicas e de aplicações médicas podem ser utilizadas, estas são chamadas pelo acrônimo ISM. A equação que descreve a densidade de energia coleta é dada por:

$$S = P_{EIRP} \left( \frac{1}{4\pi d^2} \right) \tag{3}$$

Sendo  $P_{EIRD}$  a potência efetiva irradiada e d a distância até o transmissor em um ambiente de espaço livre.

#### 2.4 Antenas

Antenas de radiofrequência são utilizadas para captar sinais na banda de 10<sup>4</sup> a 10<sup>11</sup> Hertz. Estas antenas podem ser sintonizadas em frequências específicas, como aplicações de EH, ou em bandas mais abertas, como no caso de aplicações de ES, dependendo do projeto. Certamente é importante salientar que o ganho de uma antena é inversamente proporcional a sua largura de banda, ou seja, quanto mais estreita for a banda, maior o ganho da antena. Isso é útil, em aplicações como *Energy Harvesting*, quando se analisa a aplicação, ou seja, quando se pretende emitir um sinal para alimentar os circuitos em um ambiente, ou se conhece bem o espectro disponível. É interessante que este sinal seja emitido em uma única frequência para que o ganho seja máximo nas antenas sintonizadas dos receptores. Ou, em caso de coleta de energia em ambientes cujo gerador não é local, ou em casos de *Energy Scavenging*, antenas de banda mais aberta são mais úteis, pois são capazes de adquirir energia de diferentes fontes geradoras de RF.

Em termos numéricos, a potência disponibilizada por uma antena irá depender da densidade de energia e da abertura efetiva da antena, A<sub>e</sub>. Sendo a equação que descreve esta potência dada por:

$$P_{AV} = S. A_e = S. \frac{\lambda_{RF}^2}{4.\pi}. G_r = P_{EIRP}. G_r \frac{\lambda_{RF}^2}{(4.\pi.d)^2}$$

(4)

Onde

$$A_e = \frac{\lambda_{RF}^2 Gr}{4\pi},\tag{5}$$

Sendo  $G_r$  o ganho da antena e  $\lambda_{RF}$  é o comprimento de onda.

Como é possível notar, quanto maior a frequência, menor é o *range* de potência. As formas e dimensões das antenas variam muito e vários projetos distintos de antenas têm sido empregados em aplicações de *RFEH*, quanto em aplicações RFID. (PENELLA-LÓPEZ; GASULLA-FORNER, 2011).

Os receptores de baixa frequência usam acoplamentos capacitivo ou indutivo para obter potência para alimentar o circuito integrado. Nessas frequências, o comprimento de onda acaba sendo muito grande quando comparado a aplicações de alimentação a curtas distâncias. Nestes casos, o campo estaria na região chamada de *near field* (campo próximo) e poderia estar acoplado indutiva ou capacitivamente com a antena. Nessa região, a intensidade de campo decai 60 dB por década de distância. Neste trabalho, a proposta é utilizar as frequências disponíveis no ambiente, ou seja, a antena utilizada no circuito deverá atuar na região de *far field* (campo distante).

Distâncias além de 2λ são consideradas como a região de campo distante, onde a onda eletromagnética não pode retroagir sobre a antena que a gerou. No entanto, a energia irradiada por RF ainda pode ser coletada, usando uma estrutura ressonante apropriada (antena). Na região do campo distante, a intensidade do campo é atenuada em 20 dB por década de distância, ou 1/d, conforme Penella-López e Gasulla-Forner (2011).

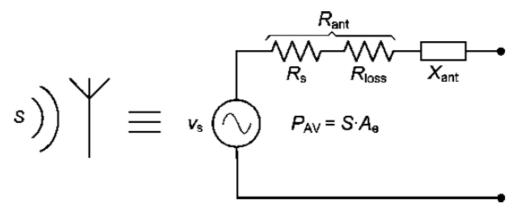

Uma antena pode ser representada como uma fonte de corrente alternada em série com uma impedância, em que a impedância é composta por uma resistência de perda, uma resistência de radiação e uma parte reativa. Em baixas frequências, a resistência das perdas é muito baixa e não considerada no projeto, porém em altas frequências, devido ao efeito *skin*, que ocorre quando a carga passa a se movimentar na periferia do condutor, as perdas começam a se tornar significantes e devem ser consideradas no projeto. A Figura 3 apresenta o modelo elétrico de uma antena receptora em que S é a fonte geradora de potência e X<sub>ant</sub>, dependendo do tipo de antena, pode ser indutivo ou capacitivo.

Figura 3 - Modelo equivalente de uma antena de RF

Fonte: Penella-López e Gasulla-Forner (2011, p. 127).

A amplitude da tensão gerada pela antena quando em sintonia com o sinal gerado cresce de acordo com a potência disponível e a resistência da antena, o que é bom para aumentar o nível de tensão e reduzir as perdas no retificador devido ao chaveamento dos transistores. A tensão gerada é dada pela expressão

$$\hat{v}_s = 2\sqrt{2R_s P_{AV}} \tag{6}$$

Esta relação se torna útil quando é necessário aumentar o nível de tensão do sistema, mas não é possível modificar a potência emitida pelo irradiador. Nesse caso, arranjos de antenas podem ser utilizados para aumentar a resistência da mesma e, consequentemente, a tensão gerada. O fator de qualidade (Q) de uma rede casada é a razão entre a frequência de ressonância ( $f_r$ ) e a largura de banda (BW) do circuito em - 3 dB (BW); assim, quanto maior o Q, menor a largura de banda. Se largura de banda for muito estreita, um pequeno desvio em  $f_r$  causará uma queda de energia expressiva na entrada do retificador; portanto, a largura de banda deve ser mantida suficientemente grande de forma que a potência de entrada não sofra grandes variações. O circuito com a rede de casamento do indutor de derivação é um circuito paralelo RLC com uma resistência que é a associação paralela de  $R_S$  e  $R_{in}$  ( $R_P = R_S \parallel R_{in}$ ) (PENELLA-LÓPEZ; GASULLA-FORNER, 2011).

O fator de qualidade pode ser modelado através da equação:

$$Q = \frac{f_r}{BW} = R_p C_{in} \omega_r = \frac{R_p}{\omega_r L_s}$$

(7)

Através desta equação, é possível modelar o circuito de entrada para que tenha um casamento de impedâncias adequado para a largura de banda e frequências de interesse. A rede LC consegue incrementar a tensão da antena quando bem sintonizada, o que se torna bastante útil quando se tem uma baixa potência disponível ou quando não se consegue aumentar a tensão

de saída da antena aumentando a impedância dela. Nesse caso, é possível modelar a rede através das equações seguintes, onde é possível perceber uma dependência de  $L_m$  de  $C_{in}$ , o que não acontece em  $C_m$ .

$$C_m = \frac{1}{R_S \omega_r} \sqrt{\frac{R_S}{R_{in} - R_S}} \tag{8}$$

$$L_m = \frac{R_{in}}{\omega_r} \frac{1}{R_{in}C_{in}\omega_r + \sqrt{\frac{R_{in} - R_S}{R_S}}}$$

(9)

Através dessas equações, é possível obter uma relação entre V<sub>in</sub> e V<sub>S</sub> na ressonância.

$$H(\omega_r) = \frac{v_{in}(\omega_r)}{v_S(\omega_r)} = \frac{1}{2} \sqrt{\frac{R_{in}}{R_S}}$$

(10)

Onde Q pode ser escrito também como:

$$Q = \frac{1}{2} \left[ R_{in} C_{in} \omega_r + \sqrt{\frac{R_{in} - R_S}{R_S}} \right] \tag{11}$$

Evidentemente, além de uma antena adequada, a fonte geradora deve ser bem conhecida em um sistema de coleta de energia de radiofrequência. Dessa forma é possível identificar a capacidade de carga do dispositivo e definir quais topologias são mais adequadas para a aplicação.

#### 2.5 Disponibilidade de energia

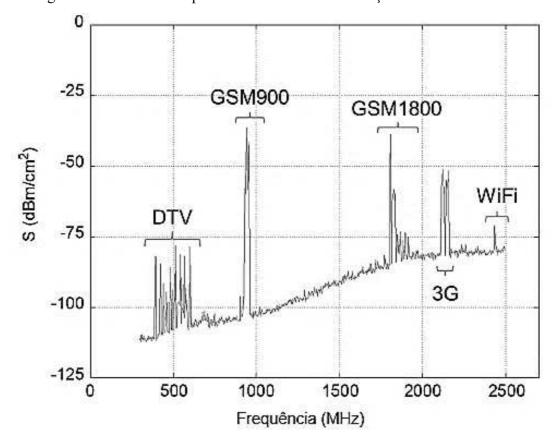

Para garantir que haverá energia disponível para ser coletada no ambiente, é importante conhecer o espectro de radiofrequência. A grande maioria dos dispositivos IoT está e estará disposta nas grandes cidades, onde a atividade humana é mais intensa. Além disso, dentro das grandes cidades, é importante conhecer a energia disponível para coleta tanto dentro como fora das construções. Este fator é de extrema importância para a escolha do tipo de coletor de energia, bem como para a definição se será ou não necessário utilizar um dispositivo para "iluminar" os *harvesters*, ou seja, para gerar sinal RF exclusivamente para alimentar os dispositivos de coleta de energia.

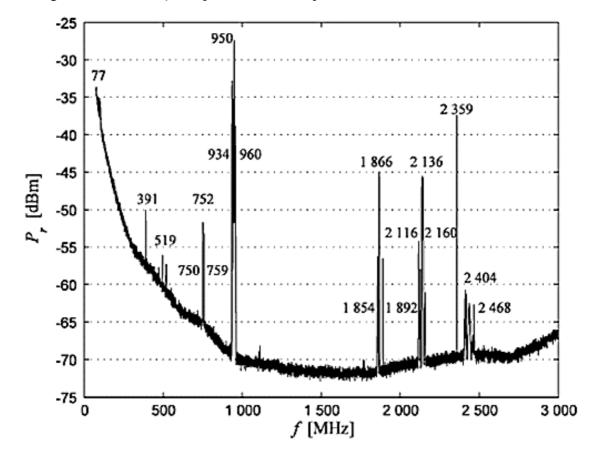

Os estudos de Piñuela et al. (2013) e de Barroca et al. (2013) apresentam medições dos espectros eletromagnéticos de grandes cidades; Londres, Inglaterra e Covilhã, Portugal, respectivamente. No caso deste primeiro, as medições foram realizadas em estações de metrô em regiões urbanas e semiurbanas. A Figura 4 apresenta o espectro medido do lado de fora da

estação Northfields London Underground, onde é possível observar uma grande quantidade de energia captada nas bandas GSM.

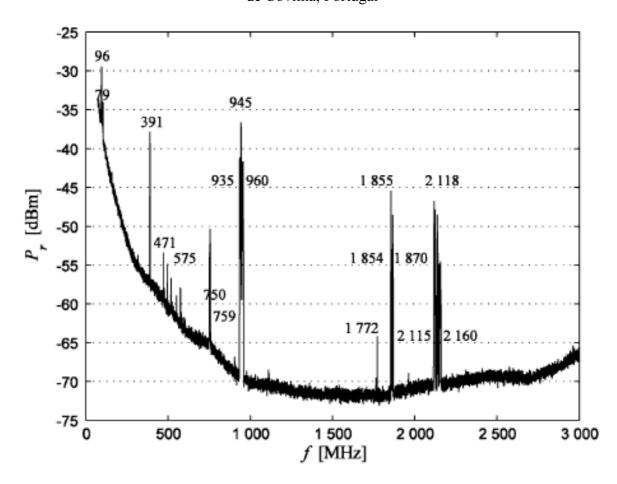

Já Barroca et al. (2013) apresentam em seu trabalho uma análise de potência disponível no espectro RF em Covilhã, Portugal. Neste trabalho, foram feitas medições em diversos pontos da cidade, tanto dentro das instalações da Universidade da Beira Interior quanto fora de construções em alguns pontos da cidade. A Figura 5 e a Figura 6 apresentam as médias de potência medidas tanto dentro da Universidade, quanto em pontos da cidade. Também através das figuras é possível identificar que as bandas GSM se destacam pela quantidade de potência disponível.

Figura 4 - Densidade de potência medida fora da estação Northfields London.

Fonte: Adaptado de Piñuela et al. (2013, p. 2717)

Figura 5 – Distribuição espectral média de potência medida dentro da Universidade.

Fonte: Barroca et al. (2013, p. 533).

Com isto, a escolha pelo desenvolvimento de circuitos para coleta de energia em frequências correspondentes às bandas GSM, principalmente, se mostra muito pertinente, visto que há potência disponível capaz de alimentar alguns dispositivos IoT de baixo consumo. Contudo, aplicações em outras bandas, como as utilizadas para Wi-Fi, por exemplo, possuem uma potência disponível mais escassa, levantando a possibilidade de utilizar equipamentos de geração de RF, ou seja, geradores de RF para iluminar estes dispositivos.

Figura 6 - Distribuição espectral média de potência medida em pontos específicos na cidade de Covilhã, Portugal

Fonte: Barroca et al. (2013, p. 533).

Para casos em que se deseje utilizar estes geradores, deve-se definir uma potência para este gerador de forma que todos os dispositivos na área que ele ilumina recebam ao menos o mínimo de energia necessária para seu funcionamento. Para estimar a potência recebida por um determinado dispositivo iluminado por uma fonte geradora de RF conhecida, utiliza-se a Lei de Friis:

$$P_{receptor} = P_{transmissor} \times G_{receptor} \times G_{transmissor} \times \left(\frac{\lambda}{4\pi d}\right)^{2}$$

(12)

Onde P é potência em Watt, G é o ganho e d é a distância da fonte geradora de RF até o *harvester*.

#### 2.6 Retificadores

Retificadores são circuitos que tem em sua entrada um sinal em corrente alternada e que o converte em um sinal de corrente contínua. Basicamente, retificadores podem ser de um único

diodo, com diodos em ponte ou multiplicadores de tensão. Todos estes circuitos operam em *broadband*, ou seja, trabalham bem em frequências entre quilohertz e mega-hertz. Para frequências acima disso, diodos *Schottky* podem ser utilizados por terem menor tempo de transição.

A Figura 7 apresenta circuitos retificadores comuns, que transformam um sinal originalmente de corrente alternada em um sinal de corrente contínua. O problema destes circuitos é que ambos têm uma perda de potência sobre os diodos. No caso de (a), a queda de tensão é igual à queda no diodo. Em (b), a queda de tensão é ainda maior, pois são dois diodos que possuem uma queda de potencial sobre eles, porém, a retificação ocorre em ambos os semiciclos do sinal de entrada. Circuitos de EH geralmente não utilizam este tipo de topologia, pois são pouco eficiente e geralmente possuem valores de queda de tensão sobre os diodos retificadores muito acima da tensão que recebem na entrada.

Vin Vout Vout Vout (b)

Figura 7 - Circuitos retificadores com diodos

Fonte: Adaptado de Penella-López; Gasulla-Forner (2011, p. 131).

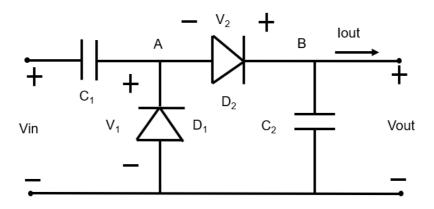

O circuito da Figura 8 é um exemplo de retificador multiplicador de tensão. Neste circuito, a retificação é feita através da multiplicação do sinal de entrada, ou seja, para uma configuração como esta, o capacitor  $C_1$  é carregado quase que até o valor de pico do sinal de entrada no semiciclo positivo. No semiciclo negativo, o diodo abre o circuito e não há circulação de corrente pelo diodo  $D_1$ , ou seja, a tensão do sinal de entrada acaba sendo somada à tensão do capacitor  $C_1$ , elevando o sinal da saída ao dobro da tensão de pico do sinal de entrada.  $D_2$  e  $C_2$  funcionam como o retificador simples com um diodo e serve para que ambos os semiciclos sejam utilizados na retificação, assim como o retificador em ponte faz.

Figura 8 - Retificador multiplicador de tensão

Fonte: Adaptado de Penella-López; Gasulla-Forner (2011, p. 131).

Esta configuração pode ser utilizada em cascata para multiplicar o sinal de entrada mais vezes, sendo que a tensão de pico da saída será equivalente à duas vezes a quantidade de estágios vezes a tensão de pico do sinal de entrada, menos a queda sobre os diodos, ou seja:

$$V_{P_{out}} = 2 \times N \times V_{P_{in}} - V_D \tag{13}$$

Quando se utiliza mais estágios de multiplicação e se substitui os diodos por transistores MOS configurados como diodos, tem-se multiplicadores de tensão em topologias Dickson ou Cockcroft-Walton, dependendo da forma de ligação em cascata dos estágios subsequentes.

## 2.6.1 Multiplicadores de tensão Dickson e Cockcroft-Walton

Estes retificadores multiplicadores são compostos por dois transistores CMOS conectados como diodos, um capacitor de elevação de tensão e um capacitor de carga, conforme Figura 9. Nestes retificadores,  $C_C$  é o capacitor de elevação de tensão,  $C_{\text{load}}$  o capacitor de carga,  $V_{\text{RFin}}$  o sinal de entrada em alta frequência e  $V_{\text{out}}$  é a tensão de saída elevada e retificada.

Figura 9 - Charge pump rectifier

VRFin

CC

NMOS

S

PMOS

Cload

Cload

Fonte: Adaptado de Mnif; Mnif e Loulou (2017, p. 1).

O que diferencia as duas topologias é a forma de conexão quando se utiliza múltiplos estágios. No retificador do tipo Dickson se utiliza um ponto comum de entrada e usa a saída do estágio anterior como referência de tensão, somando o valor de V<sub>RFin</sub> ao valor de V<sub>out</sub> do estágio anterior, como é possível notar na Figura 10.

Vin O

Figura 10 - Dickson *charge pump rectifier*

Fonte: Adaptado de Barroca et al. (2013, p. 535)

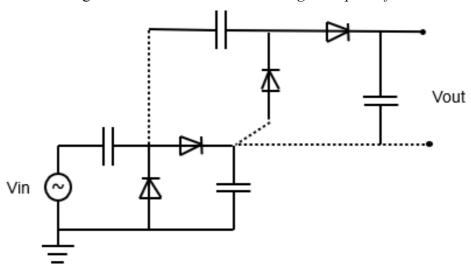

Por outro lado, o retificador do tipo Cockcroft-Walton conecta a entrada dos estágios subsequentes logo após o capacitor de entrada, como é possível notar na Figura 11, formando estágios de carga e descarga de capacitores em cada estágio de multiplicação. Como ele também utiliza a saída do estágio anterior como referência de tensão para os estágios subsequentes, o comportamento desta topologia é o mesmo da topologia do Dickson.

Figura 11 - Cockcroft-Walton Charge Pump Rectfier

Fonte: Adaptado de Barroca et al. (2013, p. 535)

A saída destes circuitos é dada por:

$$V_{out} = 2 \times N \times (V_{RFin} - V_{THP} - V_{THN})$$

(14)

Onde  $V_{THN}$  e  $V_{THP}$  são as tensões de threshold dos transistores NMOS e PMOS, respectivamente. Nesta topologia, tem-se uma perda no sinal de saída, por causa da zona morta criada por  $V_{THN}$  e  $V_{THP}$ . Porém, este tipo de retificador multiplicador serve de base para todas as demais topologias que serão tratadas a seguir. Topologias mais recentes fazem uso de técnicas de projeto que visam mitigar os efeitos dessa zona morta, tornando os retificadores mais eficientes.

## 2.6.2 Multiplicador de tensão por chaveamento ortogonal (OS-CPR)

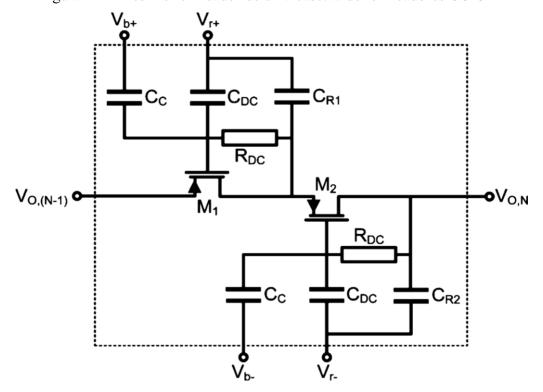

O OS-CPR proposto por Mansano (2016) utiliza transistores PMOS como chaves controladas por sinais de tensão. Este circuito é capaz de superar o efeito da zona morta, pois a tensão de entrada é superior à tensão de *threshold* graças a uma rede ressonante de elevação de tensão. Estes circuitos podem ser utilizados em cascata, assim como o multiplicador de tensão mencionado na seção 2.6.1. A Figura 12 mostra o enésimo retificador de um arranjo cascateado de retificadores.

Figura 12 - Enésimo retificador de uma cascata de retificadores OS-CPR

Fonte: Mansano (2016, p. 22).

Uma rede passiva de elevação de tensão (VBN) é necessária para fornecer ao circuito um nível de tensão na entrada que seja capaz de superar os níveis de tensão da zona morta. Além disso, um sinal de controle  $V_r$ , necessário para o funcionamento do circuito é obtido através do divisor resistivo presente na VBN. Essa rede é modelada através de um circuito ressonante série composto por uma indutância autoinduzida,  $L_A$ , pela resistência de uma antena,  $R_A$ , e um capacitor de sintonia,  $C_T$ . A Figura 13 mostra o layout de uma VBN. Esta rede pode ter a eficiência de conversão de potência (PCE) controlada por sinais de controle ( $V_r$ + e  $V_r$ -) que chaveiam o retificador de tensão, conforme Udupa, Sushma e Chaithra (2018).

Figura 13 - Modelo de circuito da voltage boosting network

Fonte: Adaptado de Mansano (2016).

A capacitância de sintonia C<sub>T</sub> é dada por:

Impedância da Antena

$$C_T = C_B + \left(\frac{C_D.C_{R,T}}{C_D + 2C_{R,T}}\right) \tag{15}$$

Sendo que C<sub>B</sub> é a capacitância de reforço, C<sub>D</sub> a capacitância do divisor de tensão capacitivo e C<sub>R,T</sub> é capacitância de entrada de retificador, para retificadores controlados. Para zerar o erro de *offset* na entrada, basta fazer a ligação de um *choke* (ligação de alta impedância em corrente alternada e baixa em corrente contínua) na entrada para induzir um curto em CC, diz Mansano (2016).

Conforme Mansano (2016), o sinal diferencial de entrada deste sistema é definido por:

$$V_r \approx \left(\frac{C_D}{2C_{R,T} + C_D}\right) V_b \tag{16}$$

Onde  $V_b$  é o sinal de controle que equivale a  $QV_A$ , sendo  $V_A$  é a tensão nos terminais da antena. E, se considerarmos  $V_{0,(N-1)}$ ,  $V_{0,N}$  e  $V_r$ - sincronizadas, então  $V_b$  e  $V_r$  controlam o chaveamento do circuito.

Se M1 estiver ligado, então M2 está desligado,  $V_{0,(N-1)} > V_{r+}$  e  $V_{b+} < V_{b-}$ , causando o carregamento de  $C_{R1}$  até aproximadamente  $(2N - 1)V_R$ . Quando M1 estiver desligado e M2 ligado,  $V_{r+} > V_{r-}$  e  $V_{b+} > V_{b-}$ , então  $C_{R2}$  é carregado até  $2NV_R$ , que é a saída do estágio N do circuito, conforme Mansano (2016).

Independentemente de qual transistor estiver ligado, os grandes sinais estão presentes nos *gates* e *sources*, fazendo com que C<sub>R1</sub> esteja constantemente sendo carregado quando M1 estiver ligado e C<sub>R2</sub> quando M2 estiver ligado. Quando em região de tríodo, estes transistores dissipam pouca potência pois a queda de tensão sobre eles na região linear é baixa. Em tempo, este tipo de circuito apresenta uma alta eficiência de conversão de energia, principalmente para cargas resistivas pequenas, segundo Mansano, Bagga e Serdijn (2013).

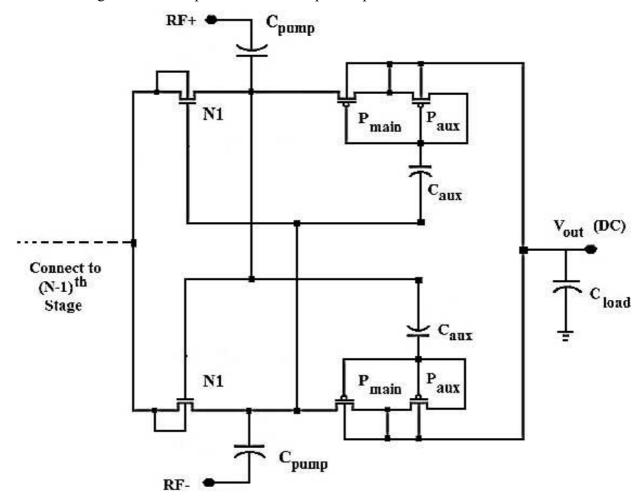

## 2.6.3 Multiplicador de tensão por acoplamento cruzado (CC-CPR)

Os CC-CPR, ou retificadores por multiplicação de tensão com acoplamento cruzado de portas, são retificadores conhecidos por conseguirem manter uma resistência baixa quando ativos e baixa fuga de corrente ao mesmo tempo. Ele é baseado em uma topologia CMOS diferencial cruzada ligada em ponte. Nesta estrutura, as portas dos transistores são influenciadas por sinais existentes nos nós *a* e *b*, conforme Figura 14.

C<sub>pump</sub>

V<sub>a</sub>

V<sub>out</sub>

C<sub>pump</sub>

Figura 14 - Multiplicador de tensão por acoplamento cruzado

Fonte: Chouhan e Halonen (2013, p. 1).

"O transistor N1 é polarizado diretamente durante o semiciclo negativo de Va, enquanto V<sub>b</sub> no semiciclo positivo fornece uma tensão de polarização positiva para o transistor N1. Isso diminui a tensão de threshold do transistor e reduz a resistência Ron" (CHOUHAN; HALONEN, 2013, tradução nossa<sup>1</sup>). De forma complementar, o contrário também é válido, quando Va é positiva e Vb negativa, o transistor é reversamente polarizado, VG diminui e o threshold aumenta, diminuindo a corrente reversa de fuga. A tensão de retificação desse sistema é dada por

$$V_{DC(out)} = 2 \times V_{RF} - V_{drop} \tag{17}$$

Onde  $V_{\text{RF}}$  é a tensão de entrada e  $V_{\text{drop}}$  a queda de tensão no transistor.

Pela equação de saída deste circuito, pode-se notar que a máxima tensão de saída ocorre quando a queda no transistor tende a zero. Além disso, assim como retificador multiplicador citado em Mansano, Bagga e Serdijn (2013), este circuito pode ser cascateado para multiplicar a tensão de saída, obedecendo a mesma equação geral do multiplicador simples. De acordo com Dai et al. (2015), a topologia de acoplamento cruzado exibe a mais alta eficiência de conversão de energia alcançável, até 65% (somente no retificador) que pode ser mantida em uma ampla faixa de entrada ajustando o tamanho do transistor, enquanto outras topologias atingem entre 46,7% e 51%.

Além disso, este circuito apresenta uma sensibilidade muito mais alta quando comparada às demais topologias apresentadas, onde esta alta sensibilidade faz com que esta topologia seja adequada para transferência de potência sem fio em um grande range, isto é, por muitos metros (KAROLAK et al., 2012).

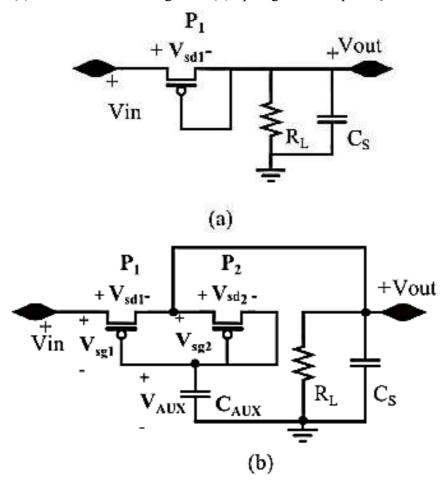

Uma modificação proposta por Chouhan e Halonen (2013) sobre o circuito multiplicador de tensão por acoplamento cruzado permite a melhoria da eficiência de conversão do retificador, devido ao cancelamento do efeito de VTH sobre o circuito. Nesta topologia, os autores adicionam um segundo transistor PMOS configurado como diodo e um capacitor auxiliar de acoplamento conectados ao transistor original. Este segundo transistor tem como função, reduzir a dependência do circuito de V<sub>TH</sub>, fazendo com que G<sub>V</sub> seja aumentado. A Figura 15 mostra a modificação proposta por Chouhan e Halonen (2015). Na Figura 16 é possível observar a topologia do retificador por multiplicação de tensão com acoplamento cruzado modificado completa.

<sup>&</sup>lt;sup>1</sup> The transistor N1 is forward biased during negative half cycle of Va, while Vb in positive half cycle gives a positive gate bias voltage to N1 transistor. This decreases the threshold voltage of the transistor and reduces the on resistance.

A ideia deste arranjo é que durante a condução direta, o circuito retifique o sinal de entrada em RF usando o princípio de cancelamento de V<sub>TH</sub>. Da mesma forma, quando o sinal de entrada RF negativo é aplicado, o diodo entra em um modo de condução reversa; idealmente na condução reversa, não deve haver vazamento de corrente.

Figura 15 – (a)Transistor PMOS original e (b)topologia de compensação de tensão de limiar

Fonte: Adaptado de Chouhan e Halonen (2015, p. 235)

Na prática, devido à resistência finita de um diodo desligado, o capacitor de armazenamento ( $C_S$ ) começa a atuar como fonte de tensão e, portanto, começa a descarregar, o que é indesejável e incontrolável. No circuito exposto, a carga necessária para desenvolver  $V_{AUX}$  é obtida de condução reversa e direta. Assim, podemos dizer que a presença de  $C_{AUX}$  preserva alguma parte da carga, que geralmente é perdida durante a condução reversa nos retificadores convencionais. Ou seja, tem-se:

$$V_{AUX} = C_{AUX} \times (Q_{direta} + Q_{reversa})$$

(18)

No circuito de Chouhan e Halonen (2013), a tensão de saída é definida por:

$$V_{OUT} = V_{0V2} + V_{AUX} (19)$$

E a tensão de entrada por:

$$V_{IN} = V_{0V1} + V_{OUT} (20)$$

Onde  $V_{0V1}$  e  $V_{0V2}$  são as tensões de *Overdrive* através do transistor principal e auxiliar, respectivamente e  $V_{aux}$  é a tensão sobre o capacitor auxiliar. Fazendo a subtração destas equações, obtemos:

$$V_{OUT} = \frac{1}{2} \left( (V_{0V2} - V_{0V1}) + V_{IN} + V_{AUX} \right)$$

(21)

E, sabendo que

$$V_{0V} = V_{th} + \sqrt{\frac{2I_D}{\beta}} \tag{22}$$

Figura 16 - Multiplicador de tensão por acoplamento cruzado modificado

Fonte: Adaptado de Chouhan e Halonen (2013, p. 3)

Ao substituir V<sub>0V</sub> em V<sub>OUT</sub> e obtém-se:

$$V_{OUT} = \frac{1}{2} \left( (V_{th2} - V_{th1}) + \left( \sqrt{\frac{2I_{D1}}{\beta}} - \sqrt{\frac{2I_{D2}}{\beta}} \right) + V_{IN} + V_{AUX} \right)$$

(23)

Mostrando que o circuito se torna independente das tensões de *threshold* dos transistores, aumentando sua capacidade de conversão em tensão CC. Casamento de impedância.

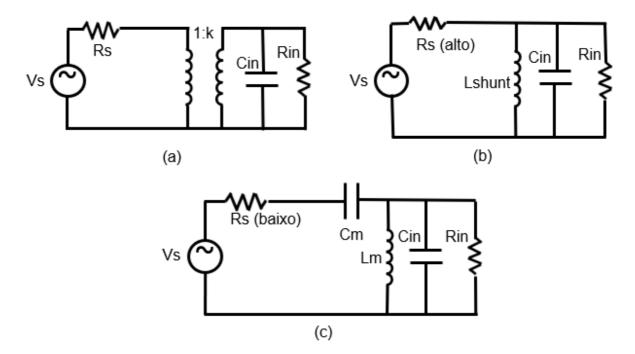

Para que se tenha um rendimento ótimo, é necessário que haja casamento entre as impedâncias da antena e do circuito ao qual ela está conectada, ou seja, quando a antena enxerga em seus terminais de saída uma impedância que seja o conjugado de sua própria impedância:  $Z_{ant} = R_S - jX_{ant} \mbox{ (PENELLA-LÓPEZ; GASULLA-FORNER, 2011). A Figura 17 mostra alguns circuitos comumente utilizados para fazer este casamento de impedâncias.}$

Figura 17 - Circuitos de casamento de impedâncias típicos utilizados em RFEH

Fonte: Adaptado de Penella-López e Gasulla-Forner (2011, p. 128).

Em (a), pode-se observar um circuito de transformador, utilizado para valores intermediários de  $R_s$ ; em (b) um indutor shunt para altos valores de  $R_s$  e em (c) uma rede LC para baixos valores de  $R_s$ .

É comum que se use um balun logo após a antena para fazer o casamento de impedância entre o circuito e a antena, geralmente quando se usa uma antena comum, assimétrica, em um circuito diferencial.

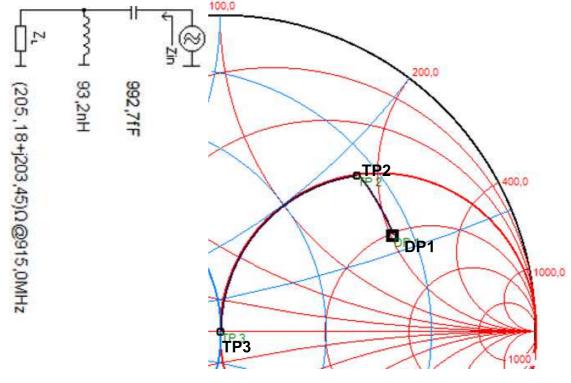

Geralmente, quando o circuito conta com uma rede ressonante na entrada para elevação de tensão, se faz necessário um circuito de casamento de impedâncias entre esta rede ressonante e o balun ou diretamente a antena. Nesse caso, se faz uso da Carta de Smith para encontrar o circuito adequado que consiga casar as impedâncias de entrada do circuito com a de saída do balun ou antena.

Redes de casamento de impedância tem sua complexidade de implementação devido aos cálculos necessários para fazer com que o casamento de impedâncias seja adequado. Mesmo assim, o uso de redes de casamento de impedância fixas torna o projeto limitado, uma vez que a impedância equivalente do circuito depende da potência de entrada e a eficiência de conversão de energia (PCE) do sistema acabará sendo diminuído devido a uma incompatibilidade de impedâncias causada por variação da potência de entrada. Portanto, uma rede de correspondência sintonizável fornece uma solução adequada para compensar a diferença de impedância de modo a melhorar o PCE do sistema em uma ampla faixa de potência de entrada. (WANG *et al.*, 2017). Essa sintonia pode ser realizada utilizando uma técnica de chaveamento de capacitores, tanto na rede de casamento quanto no circuito ressonante, uma vez que o retificador é capaz de funcionar com praticamente qualquer frequência de entrada, sendo limitado à velocidade de chaveamento dos MOSFET utilizados. Para isso, podem ser utilizados circuitos de gerenciamento de energia, geralmente microcontrolados.

## 2.7 Gerenciadores de energia

Reduzir o consumo de energia dos circuitos integrados CMOS tem sido um tema de grande interesse nos últimos anos. Muitos estilos lógicos foram propostos nas últimas décadas para atender a essa necessidade, mas eles geralmente trocam energia por desempenho (BOZORGZADEH; ZHIAN-TABASY; AFZALI-KUSHA, 2008). Gerenciadores autônomos de energia podem ser usados para garantir que os sistemas operem sempre no ponto ótimo, garantindo a maior eficiência de conversão de energia. Esses gerenciadores podem ser analógicos ou microcontrolados.

O gerenciamento de energia pode ser considerado um processo comum envolvendo retificador, multiplicador de tensão e armazenadores (CANSIZ; ALTINEL; KURT, 2019). Por isso, Unidades de Gerenciamento de Energia (PMU) são utilizadas em muitos EH, como em Ababneh, Perez e Thomas (2017), Jung, Jang e Choi (2017), Kansal *et al.* (2007), Kim *et al.* (2014), Piñuela, Mitcheson e Lucyszyn (2013) e Popovic *et al.* (2014). A PMU permite o

monitoramento dos níveis de energia coletados pelo RFEH e fornece o controle de carga e proteção de carga dos dispositivos de armazenamento de energia.

## 2.8 Armazenadores de energia

Em sistemas de coleta de energia, se busca reduzir os custos com implantação e manutenção dos dispositivos, dessa forma, o uso de baterias deve ser feito apenas quando não há outra opção. Uma forma de fortalecer a autonomia energética desses sistemas é utilizar a captação de energia do ambiente juntamente a uma unidade de armazenamento de energia. Em comparação com baterias, ultra capacitores fornecem uma alternativa interessante para armazenamento de energia em aplicações onde uma longa vida útil é necessária ou em ambientes severos (temperaturas extremas) com a vantagem adicional de não apresentar problemas de segurança (EL MAHBOUBI *et al.*, 2018). Com o uso de sensores com consumo cada vez menor, a energia necessária para seu funcionamento, por consequência, acaba sendo menor e, o dispositivo de armazenamento de energia pode ser um capacitor. Esse capacitor pode ser tanto integrado no *chip*, quanto externo a ele, dependendo da quantidade de energia necessária.

Para se ter uma estimativa de quanta energia é necessária, deve-se conhecer os parâmetros de energia disponível no ambiente em que será instalado, e eficiência de conversão do EH, o tempo de carregamento do armazenador de energia, a frequência de ativação do dispositivo para transmissão de dados e o consumo do dispositivo para realizar toda a tarefa que lhe é demandada. Dessa forma, o tempo de carga, de acordo com a potência disponível na entrada, deve ser inferior ao tempo entre transmissões, para garantir que o dispositivo não falhe no meio de uma transmissão. Da mesma maneira, a capacidade de carga do armazenador deve ser maior que a demanda do dispositivo alimentado por ele, levando em consideração todas as perdas pela conversão de energia.

## 2.9 Conceitos básicos sobre circuitos integrados CMOS e sua fabricação

Circuitos integrados analógicos, assim como toda a eletrônica analógica, foram os primeiros a serem desenvolvidos. Porém, com a grande aceleração da digitalização dos sistemas de controle e, consequentemente, dos circuitos integrados, a integração analógica acabou perdendo espaço. Contudo, atualmente existe uma grande procura por projetistas analógicos, pois, por mais avançada que esteja a digitalização dos dispositivos, ainda existem muitas

aplicações que não são possíveis de digitalizar, ou a digitalização faz com que se perca muita qualidade. Enquanto muitos tipos de processamento de sinais de fato migraram para o domínio digital, circuitos analógicos tem se provado fundamentalmente necessários em muitos sistemas complexos e de alta performance. (RAZAVI, 2016)

Ainda de acordo com Razavi (2016), nas últimas décadas, os circuitos CMOS evoluíram de circuitos de baixa velocidade, complexidade, sinais baixos e alta tensão para tecnologias de alta velocidade, complexidade, baixa tensão e sinais combinados. O que demonstra evolução na tecnologia analógica em um mundo tecnológico que migra para uma dominância de sistemas digitais. Com a evolução dos transistores, que ficam cada vez menores, a interação entre as diferentes regiões dos circuitos integrados, assim como suas não idealidades, limita tanto a velocidade quanto a precisão deles, causando uma grande dependência do layout e encapsulamento em circuitos integrados analógicos.

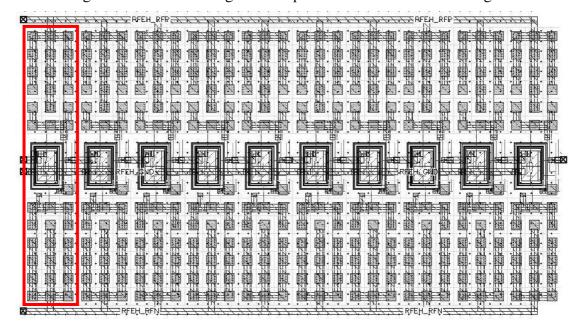

"Cada esquema de circuito projetado precisa ser transformado em um *layout* que consiste nas representações geométricas de componentes de circuito e suas interconexões" (SEDRA e SMITH, 2007). Para implementar estes circuitos em geometrias de construção de circuitos integrados, os projetistas contam com *softwares* de desenho assistido por computador (CAD). Estas aplicações, hoje em dia, já são capazes de fazer o roteamento das trilhas de forma semiautomática ou até mesmo completamente automática, o que acaba auxiliando e tornando o desenvolvimento mais rápido. Porém, o projetista deve ser capaz de corrigir e melhorar o roteamento feito pelo *software* para garantir uma melhor eficiência do circuito e redução de processos de fabricação, se possível. Assim como em projeto de placas de circuito impresso, um bom projeto de circuito integrado deve conter o mínimo de camadas possíveis, para reduzir o custo de fabricação e a dificuldade de implementação, além de evitar a adição de variáveis parasitas no circuito.

Aplicações CMOS demandam muita atenção no *layout* dos componentes dos circuitos integrados para garantir altos índices de rendimento de fabricação, ou *yield*. Dispositivos CMOS analógicos requisitam ainda mais atenção e precauções de layout, pois são muito mais suscetíveis a problemas de ruído, *mismatch* (variações físicas aleatórias nas propriedades de componentes idênticos) e *crosstalk* (interferência elétrica indesejada que um circuito ou parte de um circuito causa em outro), conforme Razavi (2016).

Transistores muito grandes podem causar variação de resistência de uma ponta a outra de seus corpos, além de ocuparem uma área maior no *chip*, para isso, utiliza-se uma técnica chamada *multifingering*, que consistem em dividir as junções S/D (fonte/dreno) em ramos menores (*fingers*). Como regra geral, a largura de cada *finger* é escolhida de modo que a

resistência do *finger* seja menor que a transcondutância inversa associada a ele. Em aplicações de baixo ruído, a resistência da porta deve ser de um quinto a um décimo de 1/g<sub>m</sub> (RAZAVI, 2016).

Problemas com simetria podem ser muito significativos em circuitos diferenciais introduzindo *offsets* (diferenças de níveis de tensão) de entrada, por exemplo, o que limita a sensibilidade e aumenta o menor sinal que pode ser detectado. *Layouts* simétricos são capazes de reduzir o efeito do ruído de modo comum e até mesmo não linearidades. Componentes *dummies*, que são componentes não conectados ao circuito usados apenas para preencher espaços, podem ser utilizados para tornar *layout*s assimétricos mais simétricos, preenchendo espaços periféricos dos circuitos.

Outro problema comum que se encontra ao trabalhar com *layout* analógico em dispositivos CMOS são as interconexões entre os componentes dos circuitos. Diferentemente de tecnologias CMOS mais antigas, em que se tinha apenas uma camada de metal para fazer as interconexões, tecnologias como a utilizada neste trabalho possuem até cinco *layers* (camadas) para roteamento. Um dos problemas que podem ser encontrados ao se trabalhar com vários metais é o surgimento de capacitâncias parasitas em trilhas paralelas ou que se cruzam em partes do circuito. Estas capacitâncias surgem naturalmente pois as trilhas são materiais condutivos percorridos por carga elétrica com camadas isolantes entre si, como óxido, por exemplo. O uso de técnicas como roteamento diferencial pode reduzir problemas de *crosstalking*, por exemplo, convertendo isso em distúrbios de modo comum, que acabam sendo ignorados pelo circuito. Trilhas *dummy* podem ser incluídas ao *layout* para criar capacitâncias de sobreposição entre trilhas de sinal para mitigar o acoplamento indesejado entre elas, conforme Razavi (2016).

Tecnologias CMOS mais modernas utilizam substratos P levemente dopados para evitar problemas de *latch up*, porém essa alta condutividade do substrato acaba proporcionando ao circuito uma possibilidade de conexões entre vários dispositivos do circuito, podendo corromper a integridade de alguns sinais. O acoplamento pelo substrato é um grande aspecto a se considerar em dispositivos de sinal misto. Para mitigar esta característica do substrato, podese utilizar "*guard rings*", que são anéis fechados condutivos utilizados para isolação do substrato, construídos ao redor de dispositivos como transistores, ou outros elementos sensíveis. Este elemento é de grande importância pois consegue isolar os componentes dentro dele de ruídos de corrente oriundos do substrato. Outra técnica de isolação que pode ser utilizada é a criação de poços dentro de poços, por exemplo, criar um poço P dentro de um poço N em um substrato P, dessa forma, os componentes que estiverem dentro desse poço mais interno estarão totalmente isolados dos componentes que estiverem conectados diretamente ao substrato.

Em algumas implementações de circuitos integrados onde há uma grande área de material condutor, pode ocorrer o chamado efeito antena. Este efeito é causado pelo fato de ondas eletromagnéticas serem captadas pelo material condutor como uma antena, principalmente durante as etapas de fabricação, causando variações de tensão no material, podendo ainda danificar o circuito. "Por essa razão, tecnologias CMOS submicrométricas tipicamente limitam a área total de algumas geometrias, assim minimizando a probabilidade de o óxido do gate ser danificado" (RAZAVI, 2016, tradução nossa²). Isso pode ser observado em capacitores, por exemplo, que são componentes com grandes áreas de material condutivo. Quando áreas grandes de material condutor são inevitáveis ao circuito, descontinuidades são implementadas de forma a reduzir o efeito antena. Para isso, faz-se o interfaceamento, por exemplo, entre metal 1 e metal 2, além de essa grande área não ser ligada diretamente à porta do transistor, para evitar danos ao óxido.

Cada processo é caracterizado pelo comprimento mínimo de canal,  $L_{\text{mín}}$ ; e, assim, por exemplo, em um processo de 0,18 µm, o menor transistor tem um comprimento de canal L=180 nm (SEDRA; SMITH, 2007). Comumente não se utiliza o tamanho mínimo da tecnologia para a construção dos transistores, pois variações no processo podem causar diferenças entre transistores e gerar efeitos indesejados no circuito; para minimizar este efeito, é usual dimensionar o L dos transistores mínimos com valores ligeiramente maiores que a dimensão mínima da tecnologia. Por exemplo, para uma tecnologia de 180 nm, é usual utilizar tamanhos mínimos de L para os transistores em torno de 220 nm.

Outro ponto a ser considerado é o fato de a capacitância do óxido,  $C_{ox}$ , aumentar de acordo com a redução da espessura do óxido,  $t_{ox}$ , que reduz com o comprimento do canal. Além disso, a mobilidade superficial,  $\mu$ , decresce de acordo com a redução da tecnologia, sendo que  $\mu_p$  reduz mais expressivamente que  $\mu_n$ , causado a grande discrepância entre as taxas de redução dos dois parâmetros. A transcondutância acaba acompanhando de forma inversa a redução da mobilidade superficial, pois  $C_{ox}$  tem a mesma magnitude em ambos os transistores – canal p e canal n. A transcondutância é dada em função de  $C_{ox}$  e  $\mu$ , sendo dada por  $k'_p = \mu_p.C_{ox}$  para o transistor canal p e  $k'_n = \mu_n.C_{ox}$  para o transistor canal n.

Os limiares de tensão reduzem de forma discreta em relação à tecnologia quando comparado com as magnitudes de  $V_{DD}$ . Esses limiares baixam, por exemplo, de 0,7 V para 0,48 V, enquanto  $V_{DD}$  reduz de 5 volts para 1,8 volt. Essa redução é essencial para evitar que o campo elétrico em pequenos dispositivos atinja valores muito elevados. Além disso, reduzir

<sup>&</sup>lt;sup>2</sup> For this reason, submicron CMOS Technologies typically limit the total area of such geometries, thereby minimizing the probability of gate oxide damage.

V<sub>DD</sub> é fundamental para manter a dissipação de energia tão baixa quanto possível (SEDRA e SMITH, 2007).

A redução da folga entre os valores de  $V_{DD}$  e  $V_t$  tornou-se um grande desafio para o projetista de CI, visto que  $|V_{GS}| = |V_t| + |V_{0V}|$ , onde  $V_{0V}$  é a tensão de limiar necessária para manter  $|V_{GS}|$  razoavelmente baixa. Outro efeito observado em tecnologias de escalas nanométricas, é a influência pronunciada do efeito de modulação do comprimento do canal. Assim,  $V_A$  vem diminuindo, o que, combinado com a diminuição do comprimento, tem feito que a tensão de Early  $V_A = V_A$ .L se torne muito pequena. De forma correspondente, os MOSFET de canal curto exibem baixas resistências de saída (SEDRA e SMITH, 2007).

Quanto à operação do MOSFET, para operar no modo ativo, duas condições devem ser satisfeitas. Primeiramente, o canal deve ser induzido, ou seja,  $v_{GS} \ge V_t$ , para isso, faz-se  $v_{GS} = V_t + v_{0V}$ . Com isso, é necessário estrangular o canal no dreno, fazendo  $v_{GD} < V_t$ , ou, de forma equivalente,  $v_{DS} \ge V_{0V}$ . Quanto à corrente no dreno, tem-se:

$$i_D = \frac{1}{2} \mu_{\rm n} C_{OX} \frac{W}{L} (v_{GS} - V_t)^2 \left( 1 + \frac{v_{DS}}{V_A} \right), \tag{24}$$

Onde  $v_{GS} - V_t = v_{0V}$ . Não há corrente na porta, afinal o MOSFET é um dispositivo controlado por tensão.

Outros parâmetros importantes para o projeto de transistores CMOS são a transcondutância  $g_m$  dada pelas equações 5, 6 e 7.

$$g_m = I_D / \left(\frac{V_{0V}}{2}\right) \tag{25}$$

$$g_m = (\mu_n C_{OX}) \left(\frac{W}{L}\right) V_{0V}, \tag{26}$$

$$g_m = \sqrt{2(\mu_n C_{OX}) \left(\frac{w}{L}\right) I_D}.$$

(27)

A resistência de saída é a razão de  $V_A$  por  $I_D$  ou  $\frac{r_o = V_A' L}{I_D}$ . O ganho é definido por  $A_v = g_m r_o$ , podendo ser escrito como:

$$A_v = \frac{V_A}{\left(\frac{V_{0V}}{2}\right)},\tag{28}$$

ou por

$$A_{v} = \frac{V_A'\sqrt{2\mu_n C_{OX}WL}}{\sqrt{I_D}}. (29)$$

Assim se chega aos principais parâmetros de projeto: I<sub>D</sub>, V<sub>0V</sub>, L e W/L.

O dispositivo CMOS apresenta capacitâncias entre todos os seus terminais, sendo que as principais são  $C_{gs}$  e  $C_{gd}$ . "Enquanto  $C_{gs}$  tem um componente de superposição,  $C_{gd}$  é inteiramente uma capacitância de superposição. Ambos,  $C_{gd}$  e o componente de superposição de  $C_{gs}$ , são aproximadamente iguais e denotados por  $C_{ov}$ " (SEDRA; SMITH, 2007).  $C_{gs}$  pode ser calculada através da expressão:

$$C_{gs} = \frac{2}{3}WLC_{OX} + WL_{ov}C_{OX} \tag{30}$$

e C<sub>gd</sub> pela expressão:

$$C_{gd} = WL_{ov}C_{OX} \tag{31}$$

A presença dessas capacitâncias no dispositivo acaba causando limitações de frequências de operação. De acordo com Sedra e Smith (2007), no caso do MOS, fabricados com tecnologias submicrométricas, como o processo de 180 nm, alcançam valores de f<sub>T</sub> na faixa de 5GHz a 15GHz". A frequência de transição f<sub>T</sub> é dada pela expressão:

$$f_T = \frac{g_m}{2\pi (c_{gs} + c_{gd})}. (32)$$

Voltando aos parâmetros de projeto, nos projetos envolvendo MOSFET existem quatro parâmetros a serem definidos; I<sub>D</sub>, V<sub>0V</sub>, L e W/L. Destes, três podem ser atribuídos pelo *designer*. Para aplicações de circuitos analógicos, o compromisso em selecionar o comprimento L está entre os valores de alta velocidade de operação (faixa de amplificação mais larga) conseguidos com menores valores de L e maiores ganhos intrínsecos obtidos com maiores valores de L (SEDRA; SMITH, 2007).

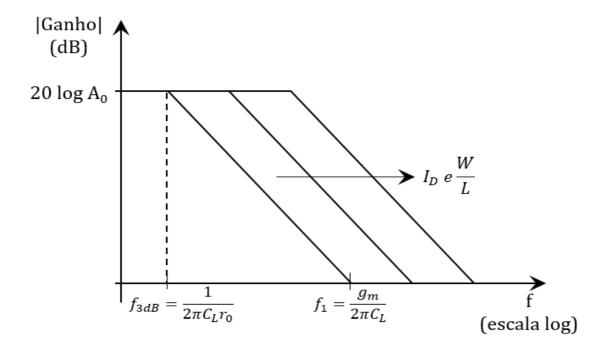

Ao parâmetro V<sub>0V</sub>, para escalas nanométricas, geralmente é atribuído valor entre 0,2 V e 0,4 V. O projetista pode optar por atribuir um valor para I<sub>D</sub> ou W/L, de acordo com a necessidade do circuito, sendo o último parâmetro calculado em função do anterior de forma proporcional. Cabe lembrar que a atribuição destes valores não tem influência sobre o ganho intrínseco do transistor, nem mesmo sobre a sua frequência de transição, porém exerce influência sobre g<sub>m</sub> e, consequentemente, sobre a relação ganho x faixa. A Figura 18 mostra como esta relação funciona; é possível notar que o ganho permanece inalterado à medida em que I<sub>D</sub> ou W/L são alterados, porém a faixa varia proporcionalmente a estes parâmetros.

Figura 18 – Faixa de operação do amplificador CMOS fonte comum

Fonte: adaptado de Sedra e Smith (2007, p. 351).

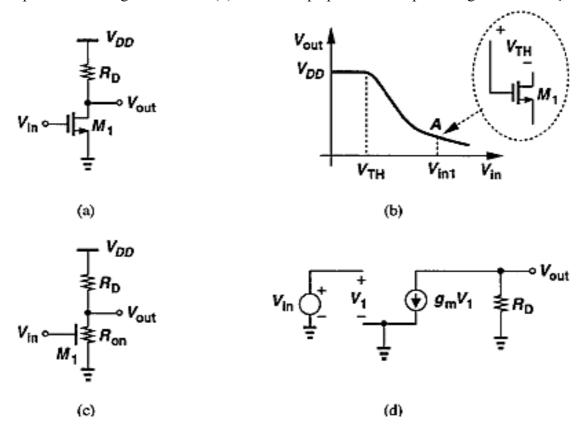

Para operar como amplificador, o transistor deve ser polarizado na região de saturação. Segundo Razavi (2016), se a tensão  $V_{GS}$  de um transistor cresce a partir de zero, o transistor está desligado e  $V_{out} = V_{DD}$ . Conforme  $V_{in}$  se aproxima de  $V_{TH}$ , o transistor começa a ligar, circulando corrente através de  $R_D$  e reduzindo o valor de  $V_{out}$ . Se  $V_{DD}$  não é excessivamente baixa, o transistor entra em saturação e tem-se:

$$V_{out} = V_{DD} - R_D \frac{1}{2} \mu_n C_{OX} \frac{W}{L} (V_{in} - V_{TH})^2$$

(33)

Onde  $V_{in} = V_{GS}$  e  $V_{TH} = V_t$ . Nesse caso, a modulação do comprimento do canal é negligenciada. Quanto maior for  $V_{in}$ , menor será  $V_{out}$ , até que  $V_{in}$  seja maior que  $V_{out}$ , onde se tem:

$$V_{in1} - V_{TH} = V_{DD} - R_D \frac{1}{2} \mu_n C_{OX} \frac{W}{L} (V_{in1} - V_{TH})^2.$$

(34)

Para  $V_{in} > V_{in1}$ , o transistor entra na região de tríodo e a expressão que modela esta região é:

$$V_{out} = V_{DD} - R_D \frac{1}{2} \mu_n C_{OX} \frac{W}{L} [2(V_{in} - V_{TH})V_{out} - V_{out}^2].$$

(35)

No caso de  $V_{out} \ll 2(V_{in} - V_{TH})$ , a equação que modela é:

$$V_{out} = \frac{V_{DD}R_{on}}{R_{on} + R_D} = \frac{V_{DD}}{1 + \mu_n C_{OX} \frac{W}{L} R_D (V_{in} - V_{TH})}.$$

(36)

As características de ganho de tensão desse circuito obedecem a expressão  $A_v = -g_m R_D$ , onde sinais grandes interferem no funcionamento do circuito, pois a transcondutância  $g_m$  varia de acordo com o sinal de entrada conforme:

$$g_m = R_D \mu_n C_{OX} \frac{W}{L} (V_{in} - V_{TH}). \tag{37}$$

Em resumo, se o ganho varia substancialmente em função do sinal de entrada, como é o caso para sinais de grande magnitude, então o circuito tende à não-linearidade. Vale salientar que para minimizar a não-linearidade, a equação de ganho deve ser pouco dependente da função do sinal como  $g_m$  (RAZAVI, 2016).

A Figura 19 mostra os esquemas necessários para o projeto de amplificadores; o modelo do circuito eletrônico, a relação entre  $V_{out}$  e  $V_{in}$ , o modelo de resistência equivalente do transistor e o modelo de pequenos sinais, respectivamente a (a), (b), (c) e (d).

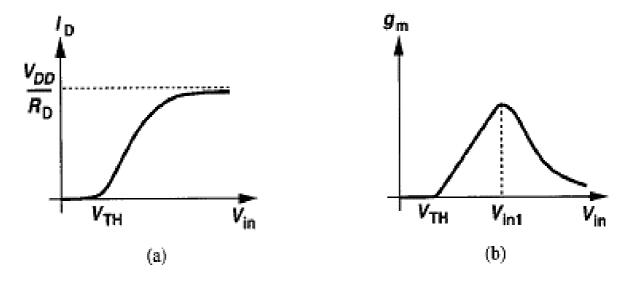

Para maximizar o ganho, faz-se uso das curvas da Figura 20 para escrever a expressão de ganho como:

$$A_v = -\sqrt{2\mu_n C_{OX} \frac{w}{L} I_D. \frac{V_{RD}}{I_D}}$$

(38)

Figura 19 – (a) Amplificador fonte comum (b) Características de entrada e saída (c) circuito equivalente na região de tríodo (d) modelo de pequenos sinais para a região de saturação

Fonte: Razavi (2016, p. 49).

O termo  $V_{RD}$  representa a queda de tensão sobre a resistência  $R_D$ . Dessa forma, pode-se observar que é possível aumentar o ganho do amplificador aumentando  $V_{RD}$  ou a relação W/L. Além disso, reduzir a corrente de dreno também aumenta o ganho do amplificador. Um tamanho maior de dispositivo acarreta maiores capacitâncias no dispositivo, e quando se eleva  $V_{RD}$ , acaba-se limita as oscilações máximas de tensão. Por exemplo, se  $V_{DD}$  -  $V_{RD} = V_{in}$  -  $V_{TH}$ , então o transistor está na borda da região de tríodo, permitindo somente oscilações muito pequenas na saída. Se  $V_{RD}$  permanecer constante e  $I_D$  for reduzida,  $R_D$  deverá aumentar, levando a uma constante de tempo maior no nó de saída. Ou seja, o circuito exibe desvantagens entre oscilações de ganho, largura de banda e tensão. Tensões baixas aumentam ainda mais essas desvantagens. Para grandes valores de  $R_D$ , o efeito da modulação do comprimento do canal do transistor se torna significativo (RAZAVI, 2016).

Figura 20 – (a) I<sub>D</sub> em função de V<sub>in</sub> (b) transcondutância em função de V<sub>in</sub>

Fonte: Razavi (2016, p. 51).

Quando o efeito de modulação do canal se torna significativo para o sinal de saída, como nos casos de amplificadores em nanoescala, então a expressão que caracteriza o sistema passa a ser, considerando a modulação de canal, a seguinte:

$$V_{out} = V_{DD} - R_D \frac{1}{2} \mu_n C_{OX} \frac{W}{L} (V_{in} - V_{TH})^2 (1 + \lambda V_{out})$$

(39)

Dessa forma, se fizermos  $\frac{\partial V_{out}}{\partial V_{in}}$ , podemos usar a aproximação de I<sub>D</sub> como:

$$I_D \approx \frac{1}{2} \mu_n C_{OX} \frac{W}{L} (V_{in} - V_{TH})^2$$

(40)

Chegando a uma expressão para o ganho do amplificador do tipo:

$$A_v = -R_D g_m - R_D I_D \lambda A_v = -g_m \left( \frac{r_o R_D}{r_o + R_D} \right)$$

$$\tag{41}$$

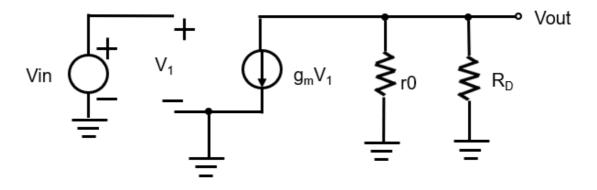

Ainda é possível resumir este processo através do modelo de pequenos sinais da Figura 21.

Figura 21 - Modelo de pequenos sinais para amplificador FC de estágio simples

Fonte: Adaptado de Razavi (2016, p. 52).

Através do modelo de pequenos sinais é possível perceber que o ganho do circuito considerando a modulação do canal é totalmente dependente de  $r_o$ ,  $R_D$  e de  $g_m$ .

### 3 METODOLOGIA

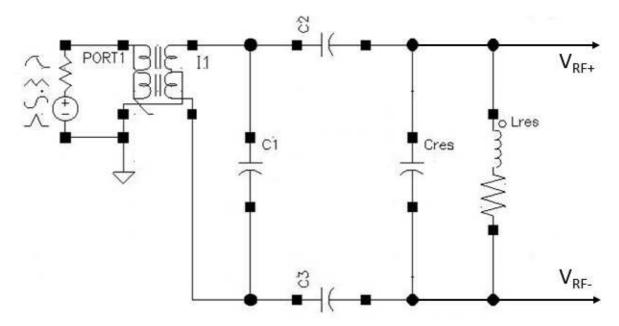

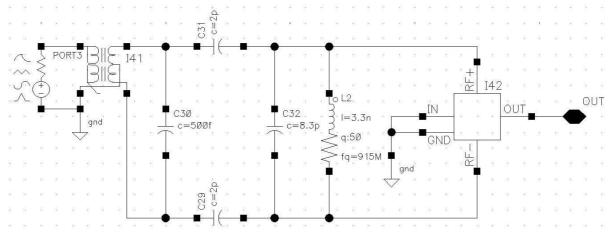

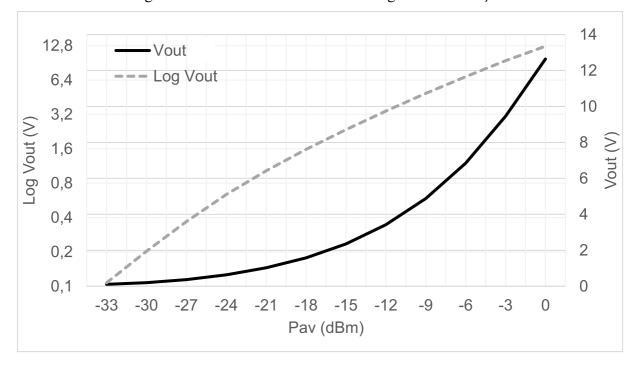

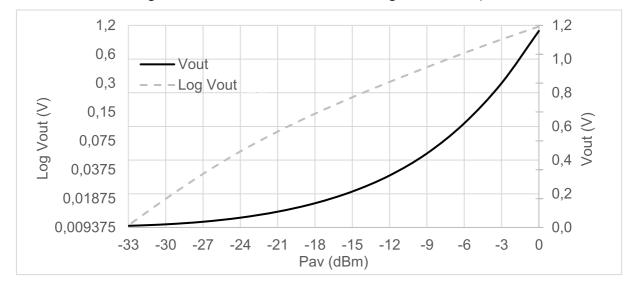

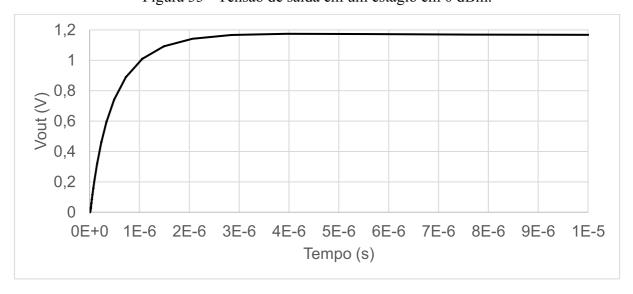

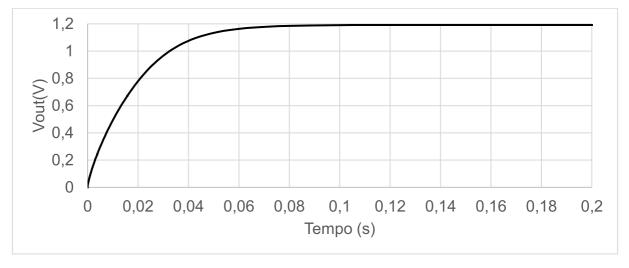

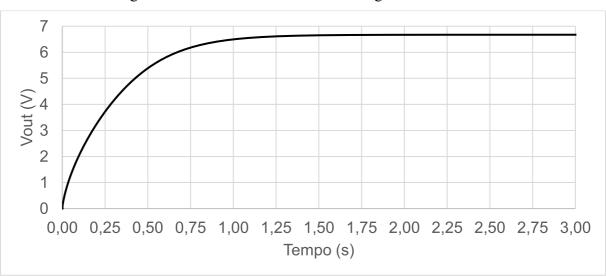

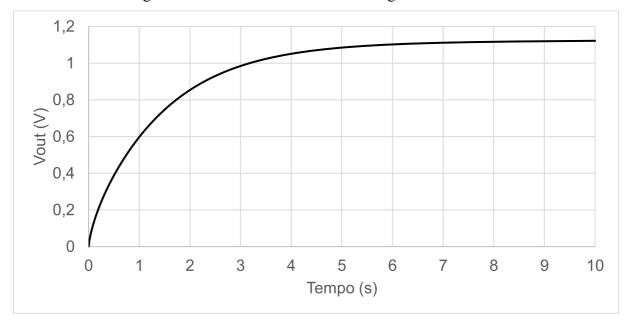

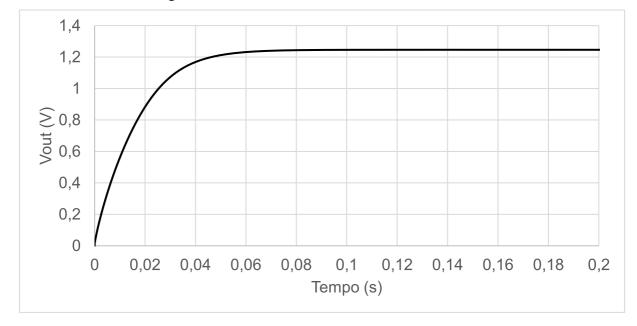

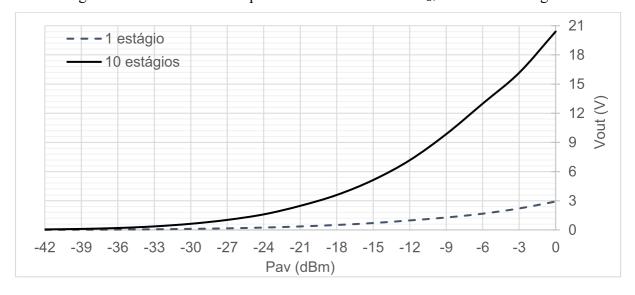

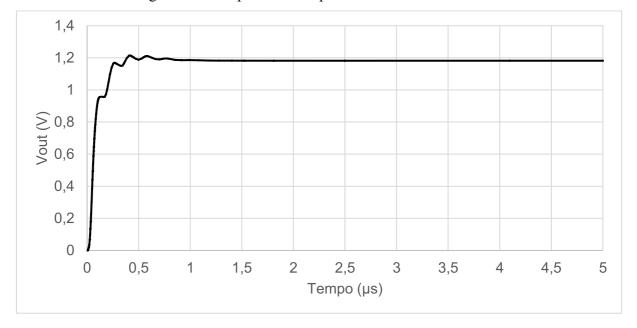

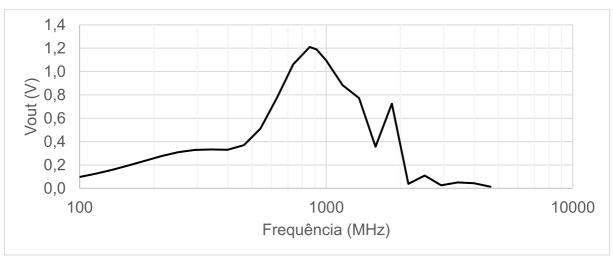

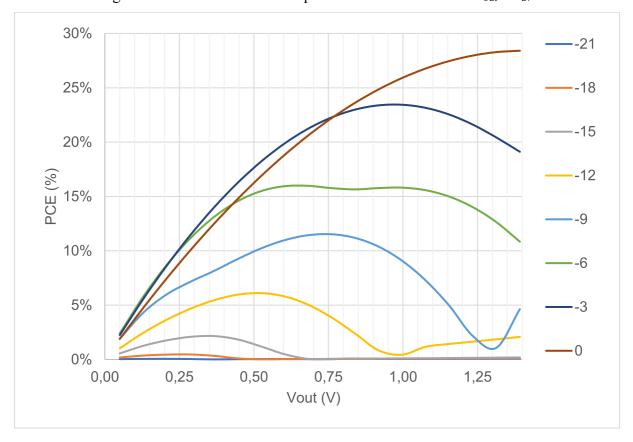

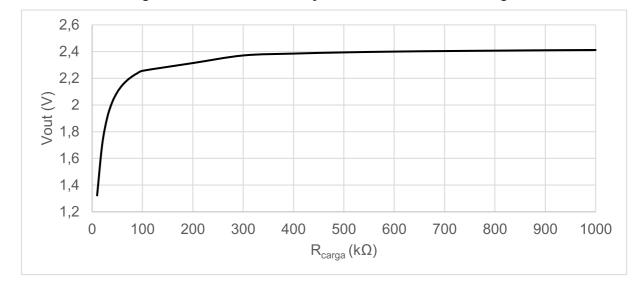

Como tecnologias relativamente recentes, apesar de a ideia de transmissão de energia por radiofrequência ser do início do século passado (TESLA, 1900), os circuitos para coleta de energia de radiofrequência ainda apresentam muitos desafios a quem os estuda, principalmente quando se trata da eficiência de conversão de energia, potência disponível no ambiente, e consumo dos dispositivos que serão alimentados com eles. Este trabalho trata do desenvolvimento de um circuito para coleta de energia na frequência ISM de 915 MHz, utilizando uma antena de RF de 50  $\Omega$ , um balun, um circuito ressonante para elevação de tensão, uma rede de casamento de impedância e um arranjo em cascata de multiplicadores de tensão em uma topologia de acoplamento cruzado de portas modificado, proposto por Chouhan e Halonen (2013).